з»“еҗҲPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜдјҳеҢ–з”өи·ҜеёғеұҖи®ҫи®Ўзҡ„еҲӣж–°ж–№жі•жҺўи®Ё

жң¬ж–ҮжҸҗеҮәдәҶдёҖз§ҚеҹәдәҺPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„з”өи·ҜеёғеұҖдјҳеҢ–ж–°ж–№жі•пјҢйҖҡиҝҮз»“еҗҲд»ҝзңҹе·Ҙе…·дёҺеёғеұҖзӯ–з•ҘпјҢжңүж•ҲжҸҗеҚҮз”өи·ҜжҖ§иғҪе’ҢеҲ¶йҖ ж•ҲзҺҮгҖӮиҜҘж–№жі•еңЁи®ҫи®ЎжөҒзЁӢдёӯеј•е…Ҙд»ҝзңҹйӘҢиҜҒзҺҜиҠӮпјҢзЎ®дҝқеёғеұҖеҗҲзҗҶжҖ§пјҢеҮҸе°‘еҗҺз»ӯи°ғиҜ•ж—¶й—ҙгҖӮеҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„й«ҳзІҫеәҰе’Ңеҝ«йҖҹе“Қеә”зү№зӮ№пјҢдјҳеҢ–з”өи·Ҝзҡ„еёғзәҝгҖҒеҷЁд»¶еёғеұҖе’Ңз”өжәҗеҲҶй…ҚпјҢд»ҺиҖҢе®һзҺ°з”өи·ҜжҖ§иғҪзҡ„жңҖеӨ§еҢ–е’ҢжҲҗжң¬зҡ„жңҖе°ҸеҢ–гҖӮжң¬ж–Үе°ҶиҜҰз»Ҷд»Ӣз»ҚиҜҘеҲӣж–°ж–№жі•зҡ„е…·дҪ“е®һзҺ°жӯҘйӘӨгҖҒдјҳеҠҝд»ҘеҸҠжңӘжқҘеҸ‘еұ•ж–№еҗ‘пјҢдёәз”өи·Ҝи®ҫи®ЎжҸҗдҫӣж–°зҡ„жҖқи·ҜгҖӮ

PGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜеңЁз”өи·ҜеёғеұҖдёӯзҡ„еә”з”ЁеҹәзЎҖ

PGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„ж ёеҝғеҺҹзҗҶ

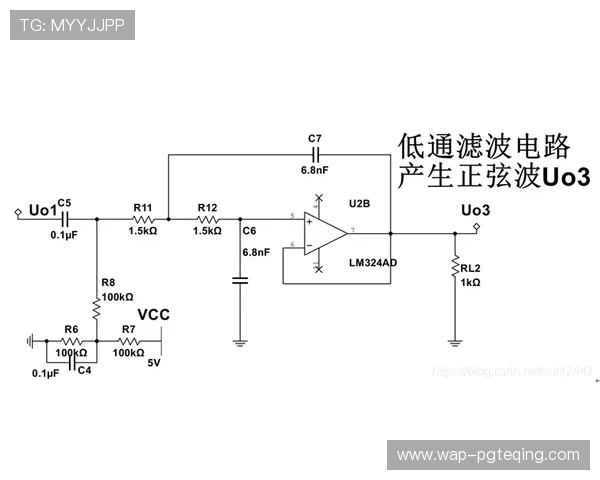

PGпјҲParasitic-aware GraphпјүзҪ‘иЎЁд»ҝзңҹжҠҖжңҜжҳҜдёҖз§ҚиҖғиҷ‘еҜ„з”ҹеҸӮж•°зҡ„з”өи·Ҝд»ҝзңҹж–№жі•гҖӮе®ғйҖҡиҝҮе»әз«ӢиҜҰз»Ҷзҡ„зҪ‘иЎЁжЁЎеһӢпјҢе°ҶеҜ„з”ҹз”өе®№гҖҒз”өйҳ»зӯүеҸӮж•°иһҚе…Ҙд»ҝзңҹдёӯпјҢзңҹе®һеҸҚжҳ з”өи·ҜеңЁе®һйҷ…е·ҘдҪңдёӯзҡ„иЎЁзҺ°гҖӮзӣёжҜ”дј з»ҹзҡ„з”өи·Ҝд»ҝзңҹпјҢPGзҪ‘иЎЁд»ҝзңҹиғҪжӣҙеҮҶзЎ®ең°йў„жөӢдҝЎеҸ·е»¶иҝҹгҖҒеҷӘеЈ°е№Іжү°е’ҢеҠҹиҖ—еҸҳеҢ–пјҢдёәз”өи·ҜеёғеұҖдјҳеҢ–жҸҗдҫӣ科еӯҰдҫқжҚ®гҖӮеҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜпјҢи®ҫи®ЎиҖ…еҸҜд»ҘеңЁеёғеұҖж—©жңҹе°ұеҸ‘зҺ°жҪңеңЁй—®йўҳпјҢжҸҗеүҚи°ғж•ҙи®ҫи®Ўж–№жЎҲпјҢйҒҝе…ҚеҗҺз»ӯзҡ„иҝ”е·Ҙе’ҢжҲҗжң¬еўһеҠ гҖӮ

PGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„дјҳеҠҝдёҺеұҖйҷҗ

PGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜе…·жңүй«ҳзІҫеәҰгҖҒеҝ«йҖҹе“Қеә”е’ҢиүҜеҘҪзҡ„йҖӮеә”жҖ§пјҢзү№еҲ«йҖӮеҗҲеӨҚжқӮз”өи·Ҝзҡ„еёғеұҖдјҳеҢ–гҖӮе®ғиғҪеңЁи®ҫи®ЎеҲқжңҹе°ұжЁЎжӢҹеҜ„з”ҹеҸӮж•°еҜ№з”өи·ҜжҖ§иғҪзҡ„еҪұе“ҚпјҢеё®еҠ©и®ҫи®ЎиҖ…еҒҡеҮәжӣҙеҗҲзҗҶзҡ„еёғеұҖеҶізӯ–гҖӮ然иҖҢпјҢиҜҘжҠҖжңҜд№ҹеӯҳеңЁдёҖе®ҡеұҖйҷҗжҖ§пјҢеҰӮд»ҝзңҹжЁЎеһӢзҡ„е»әз«ӢйңҖиҰҒеӨ§йҮҸзҡ„еҸӮж•°иҫ“е…ҘпјҢи®Ўз®—иө„жәҗж¶ҲиҖ—иҫғеӨ§пјҢзү№еҲ«жҳҜеңЁеӨ§и§„жЁЎз”өи·ҜдёӯпјҢд»ҝзңҹж—¶й—ҙ pg官方首页еҸҜиғҪиҫғй•ҝгҖӮй’ҲеҜ№иҝҷдәӣй—®йўҳпјҢдјҳеҢ–з®—жі•е’Ң硬件еҠ йҖҹжҲҗдёәжңӘжқҘз ”з©¶зҡ„йҮҚзӮ№пјҢд»ҘжҸҗеҚҮPGзҪ‘иЎЁд»ҝзңҹеңЁз”өи·ҜеёғеұҖдёӯзҡ„еә”з”Ёж•ҲзҺҮгҖӮ

з»“еҗҲPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„з”өи·ҜеёғеұҖдјҳеҢ–зӯ–з•Ҙ

еёғеұҖдјҳеҢ–зҡ„е…ій”®зҺҜиҠӮ

еңЁз”өи·ҜеёғеұҖдёӯпјҢеҗҲзҗҶзҡ„еҷЁд»¶жҺ’еёғе’Ңеёғзәҝи®ҫи®ЎжҳҜжҸҗеҚҮжҖ§иғҪзҡ„е…ій”®гҖӮеҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜпјҢеҸҜд»ҘеңЁеёғеұҖеҲқжңҹе°ұжЁЎжӢҹеҜ„з”ҹеҸӮж•°зҡ„еҸҳеҢ–пјҢжҢҮеҜјеҷЁд»¶зҡ„еҗҲзҗҶеёғеұҖпјҢеҮҸе°‘дҝЎеҸ·е»¶иҝҹе’Ңе№Іжү°гҖӮеҗҢж—¶пјҢйҖҡиҝҮд»ҝзңҹз»“жһңи°ғж•ҙз”өжәҗе’Ңең°зәҝзҡ„еёғеұҖпјҢдјҳеҢ–з”өжәҗеҲҶй…ҚзҪ‘з»ңпјҢйҷҚдҪҺеҷӘеЈ°е№Іжү°гҖӮеёғеұҖдјҳеҢ–зҡ„зӣ®ж ҮжҳҜе®һзҺ°дҝЎеҸ·и·Ҝеҫ„жңҖзҹӯгҖҒеҜ„з”ҹеҸӮж•°жңҖдҪҺгҖҒзғӯйҮҸеҲҶеёғеқҮеҢҖпјҢд»ҺиҖҢжҸҗеҚҮз”өи·Ҝж•ҙдҪ“жҖ§иғҪе’ҢеҸҜйқ жҖ§гҖӮ

д»ҝзңҹй©ұеҠЁзҡ„еёғеұҖдјҳеҢ–жөҒзЁӢ

иҜҘжөҒзЁӢеҢ…жӢ¬еҮ дёӘжӯҘйӘӨпјҡйҰ–е…ҲпјҢе»әз«ӢиҜҰз»Ҷзҡ„PGзҪ‘иЎЁжЁЎеһӢпјҢиҫ“е…ҘеҷЁд»¶еҸӮж•°е’ҢеҜ„з”ҹеҸӮж•°пјӣе…¶ж¬ЎпјҢиҝӣиЎҢд»ҝзңҹеҲҶжһҗпјҢиҜҶеҲ«жҪңеңЁзҡ„жҖ§иғҪ瓶йўҲе’ҢеҜ„з”ҹе№Іжү°зӮ№пјӣеҶҚж¬ЎпјҢж №жҚ®д»ҝзңҹз»“жһңи°ғж•ҙеҷЁд»¶дҪҚзҪ®е’Ңеёғзәҝж–№жЎҲпјҢдјҳеҢ–еҜ„з”ҹеҸӮж•°пјӣжңҖеҗҺпјҢеҸҚеӨҚиҝӣиЎҢд»ҝзңҹйӘҢиҜҒпјҢзЎ®дҝқеёғеұҖж–№жЎҲиҫҫеҲ°йў„жңҹзӣ®ж ҮгҖӮйҖҡиҝҮиҝҷз§Қд»ҝзңҹй©ұеҠЁзҡ„и®ҫи®ЎжөҒзЁӢпјҢеҸҜд»ҘеӨ§еӨ§зј©зҹӯз”өи·ҜеёғеұҖзҡ„и°ғиҜ•ж—¶й—ҙпјҢжҸҗй«ҳи®ҫи®Ўзҡ„еҮҶзЎ®жҖ§е’Ңж•ҲзҺҮгҖӮ

жңӘжқҘеҸ‘еұ•ж–№еҗ‘дёҺеә”з”ЁеүҚжҷҜ

жҠҖжңҜиһҚеҗҲдёҺжҷәиғҪеҢ–еҸ‘еұ•

жңӘжқҘпјҢPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜе°ҶдёҺдәәе·ҘжҷәиғҪгҖҒеӨ§ж•°жҚ®еҲҶжһҗзӯүжҠҖжңҜж·ұеәҰиһҚеҗҲпјҢе®һзҺ°иҮӘеҠЁеҢ–еёғеұҖдјҳеҢ–гҖӮеҲ©з”ЁжңәеҷЁеӯҰд№ з®—жі•пјҢеҸҜд»Ҙд»ҺеӨ§йҮҸд»ҝзңҹж•°жҚ®дёӯжҸҗеҸ–дјҳеҢ–зӯ–з•ҘпјҢиҮӘеҠЁи°ғж•ҙеёғеұҖеҸӮж•°пјҢжҸҗеҚҮи®ҫи®Ўж•ҲзҺҮгҖӮеҗҢж—¶пјҢз»“еҗҲдә‘и®Ўз®—иө„жәҗпјҢеҸҜд»Ҙе®һзҺ°еӨ§и§„жЁЎд»ҝзңҹеҲҶжһҗпјҢж»Ўи¶іеӨҚжқӮз”өи·Ҝзҡ„и®ҫи®ЎйңҖжұӮгҖӮиҝҷдәӣеҲӣж–°е°ҶжҺЁеҠЁз”өи·ҜеёғеұҖи®ҫи®Ўеҗ‘жҷәиғҪеҢ–гҖҒиҮӘеҠЁеҢ–ж–№еҗ‘еҸ‘еұ•пјҢжһҒеӨ§ең°зј©зҹӯдә§е“ҒдёҠеёӮж—¶й—ҙпјҢйҷҚдҪҺеҲ¶йҖ жҲҗжң¬гҖӮ

е№ҝжіӣеә”з”ЁдёҺиЎҢдёҡеҪұе“Қ

з»“еҗҲPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„з”өи·ҜеёғеұҖдјҳеҢ–ж–№жі•еңЁй«ҳжҖ§иғҪиҠҜзүҮгҖҒе°„йў‘з”өи·ҜгҖҒжЁЎжӢҹз”өи·ҜзӯүйўҶеҹҹе…·жңүе№ҝжіӣеә”з”ЁеүҚжҷҜгҖӮе®ғдёҚд»…иғҪжҸҗеҚҮз”өи·Ҝзҡ„жҖ§иғҪжҢҮж ҮпјҢиҝҳиғҪйҷҚдҪҺиғҪиҖ—е’ҢжҲҗжң¬пјҢж»Ўи¶ізҺ°д»Јз”өеӯҗдә§е“ҒеҜ№й«ҳж•ҲгҖҒдҪҺеҠҹиҖ—зҡ„йңҖжұӮгҖӮйҡҸзқҖжҠҖжңҜзҡ„дёҚж–ӯжҲҗзҶҹе’Ңжҷ®еҸҠпјҢжңӘжқҘе°ҶжҲҗдёәз”өи·Ҝи®ҫи®ЎиЎҢдёҡзҡ„йҮҚиҰҒе·Ҙе…·пјҢжҺЁеҠЁз”өеӯҗдә§дёҡзҡ„еҲӣж–°еҸ‘еұ•пјҢдёәжҷәиғҪи®ҫеӨҮгҖҒйҖҡдҝЎжҠҖжңҜе’Ңзү©иҒ”зҪ‘зӯүиЎҢдёҡжҸҗдҫӣеқҡе®һзҡ„жҠҖжңҜж”Ҝж’‘гҖӮ

з»јдёҠжүҖиҝ°пјҢз»“еҗҲPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜзҡ„з”өи·ҜеёғеұҖдјҳеҢ–ж–№жі•е…·жңүжҳҫи‘—дјҳеҠҝпјҢжңӘжқҘжңүжңӣеңЁз”өеӯҗи®ҫи®ЎйўҶеҹҹеҸ‘жҢҘжӣҙеӨ§дҪңз”ЁпјҢжҺЁеҠЁиЎҢдёҡжҢҒз»ӯеҲӣж–°дёҺеҸ‘еұ•гҖӮ